Page 53 - 电力与能源2021年第六期

P. 53

李毅铭, 等: 基于 ARM 架构的多通道振动信号采集研究 6 1

6

换时间最小为 0.41 μ s ( 在 A / D 时钟频率设置为 APB2 时钟, / DCLK 最大配置频率为 36 MHz , 超

f A

最大的 36MHz , 采样周期设置最小的 3 个 A / D 过该频率就会使采样数据精度显著下降。

时钟周期下得到), 完全满足一般情况的数据采集 对于每个要转换的通道, 都需要尽可能让采

频率需求。同时每个 A / D 包含 19 个复用通道, 样时间长一点, 以保证数据有较高的准确度, 但是

可测量来自 16 个外部源、 两个内部源和 UBAT 通 同时也会降低 A / D 的转换速率。尤其在使用多

道的信号, 在通道数上也完全符合采样需要。各 通道进行数据采集时, 合理地配置采样时间成为

个通道的 A / D 转换还有多个工作模式可供选择, 关键。本文选择将 A / D 的采样时间配置为 3 个

分别是: 单 次 转 换、 连 续 转 换、 扫 描 转 换 和 间 断 周期, 最大化 A / D 的转换速率, 降低 A / D 的总转

转换 [ 8 ] 。 换时间, 同时也满足大多数数据采集场景所需的

1.2 A / D 数据采集 精度。

A / D 的作用是将模拟信号转化为数字信号。 1.2.2 采样精度

大多数 A / D 的自身输入都是来自外部传感的电 STM32F767 的 A / D 输入范围 UREF≤U IN≤

压信号, 输出转换后的数字信号 [ 9 ] 。本文讨论的 UREF+ UREF 的输入范围: 1.8V~UDDA UDDA 为模

,

。

数据采集方法都基于 STM32F767 内部自带的模 拟电源输入, 等于 UDD 当全速运行时, 2.4 V≤

:

(

数转换器。 A / D 的关键技术参数包括采样时间、 UDDA≤UDD 3.6V ); 当低速运行时, 1.8V≤UDDA

采样精度、 分辨率和转换速率等。 ≤ UDD 3.6V )。当设置参考电压值为 3.3V 的

(

1.2.1 采样时间 情况下, 12 位 A / D 的采集精度如用于采集3.3V

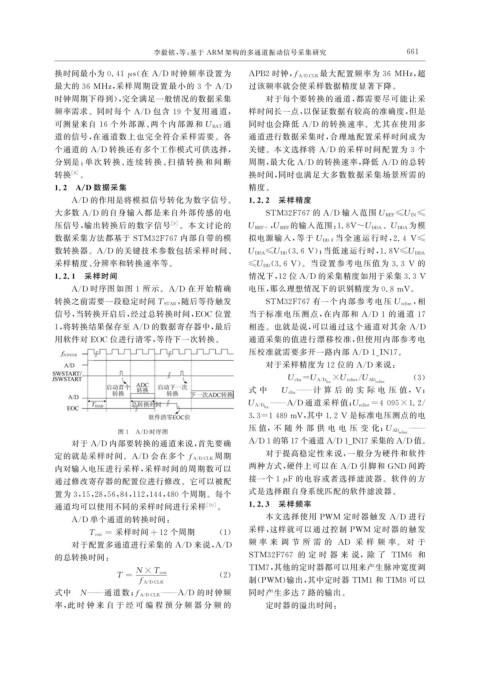

A / D 时序图如图 1 所示。 A / D 在开始精确 电压, 那么理想情况下的识别精度为 0.8mV 。

转换之前需要一段稳定时间 T STAB 随后等待触发 STM32F767 有一个内部参考电压 U refint 相

,

,

信号, 当转换开启后, 经过总转换时间, EOC 位置 当于标准电压测点, 在内部和 A / D1 的通道 17

1 , 将转换结果保存至 A / D 的数据寄存器中, 最后 相连。也就是说, 可以通过这个通道对其余 A / D

用软件对 EOC 位进行清零, 等待下一次转换。 通道采集的值进行漂移校准, 但使用内部参考电

压校准就需要多开一路内部 A / D1 _ IN17 。

对于采样精度为 12 位的 A / D 来说:

/ ( 3 )

U chx=UA / D × U refint UAD

hx refint

———计 算 后 的 实 际 电 压 值, V ;

式 中 U chx

——— A / D 通道采样值; U refint=4095×1.2 /

UA / D

hx

3.3=1489mV , 其中 1.2V 是标准电压测点的电

———

图 1 A / D 时序图 压 值, 不 随 外 部 供 电 电 压 变 化; UAD refint

对于 A / D 内部要转换的通道来说, 首先要确 A / D1的第17个通道 A / D1 _ IN17采集的 A / D 值。

定的就是采样时间。 A / D 会在多个 f A / DCLK 周期 对于提高稳定性来说, 一般分为硬件和软件

内对输入电压进行采样, 采样时间的周期数可以 两种方式, 硬件上可以在 A / D 引脚和 GND 间跨

通过修改寄存器的配置位进行修改。它可以被配 接一个 1 μ F 的电容或者选择滤波器。软件的方

置为 3 , 15 , 28 , 56 , 84 , 112 , 144 , 480 个周期。每个 式是选择跟自身系统匹配的软件滤波器。

通道均可以使用不同的采样时间进行采样 [ 10 ] 。 1.2.3 采样频率

本文选择使用 PWM 定时器触发 A / D 进行

A / D 单个通道的转换时间:

T con = 采样时间 +12 个周期 ( 1 ) 采样, 这样就可以通过控制 PWM 定时器的触发

频 率 来 调 节 所 需 的 AD 采 样 频 率。 对 于

对于配置多通道进行采集的 A / D 来说, A / D

STM32F767 的 定 时 器 来 说,除 了 TIM6 和

的总转换时间:

TIM7 , 其他的定时器都可以用来产生脉冲宽度调

N ×T con

T = ( 2 ) 制( PWM ) 输出, 其中定时器 TIM1 和 TIM8 可以

f A / DCLK

式中 N ———通道数; ——— A / D 的时钟频 同时产生多达 7 路的输出。

f A / DCLK

率, 此 时 钟 来 自 于 经 可 编 程 预 分 频 器 分 频 的 定时器的溢出时间: